FO 技术

技术概述

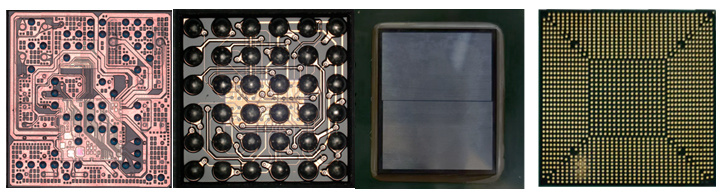

我们提供 Chip First 和 Chip Last 两种解决方案。对于芯片优先技术,第一步是将芯片面朝下放在带有粘附层的临时承载体上。第二步是用模料(EMC)覆盖模具表面。第三步是通过热释放去除粘附层和临时载体;最后,RDL 层和焊球直接在芯片和化合物表面上制造。

扇形包不仅可以使用复合材料,还能使用基材,因此扇形包扩展到另一种类型:底材扇形包(FOPoS)。

应用

我们将优化解决方案以满足客户需求。FO 技术被广泛应用于 MIC、RF、CPU、GPU 和网络。

特征

◆ 前台尺寸:32x26 毫米

◆ 将节点推进至16纳米

◆ RDL L/S:2/2um

◆ RDL 层:3 层

包类型

◆ eWLB

◆ FOPoS 芯片第一面朝下

◆ FOPoS 芯片首次正面

◆ FOPoS 芯片最后

主要优势包括

◆ 成本低于 2.5D。

◆ 良好的电气性能

◆ 高 I/O 引脚数

我们还提供广泛的产品测试开发,并在 CPU、APU、GPU、芯片组、数字音频、基带、微控制器、LCD 驱动、触摸面板驱动等领域拥有丰富经验。