奎芯科技亮相2025全球AI芯片峰会,唐睿发表Chiplet主题演讲

上海,2025年9月17日 —— 由智一科技旗下智猩猩与芯东西联合主办的2025全球AI芯片峰会今日在上海浦东喜来登由由大酒店隆重举行。本届大会以“AI大基建 智芯新世界”为主题,聚焦大模型下半场的产业破局之道,吸引了来自国内外的180余位产学研领军人物,共同探讨AI算力基础设施、芯片架构创新及未来趋势。自2018年创办以来,该峰会已成为国内AI芯片领域最具影响力的产业盛会之一,也是观察全球AI芯片格局的重要窗口。

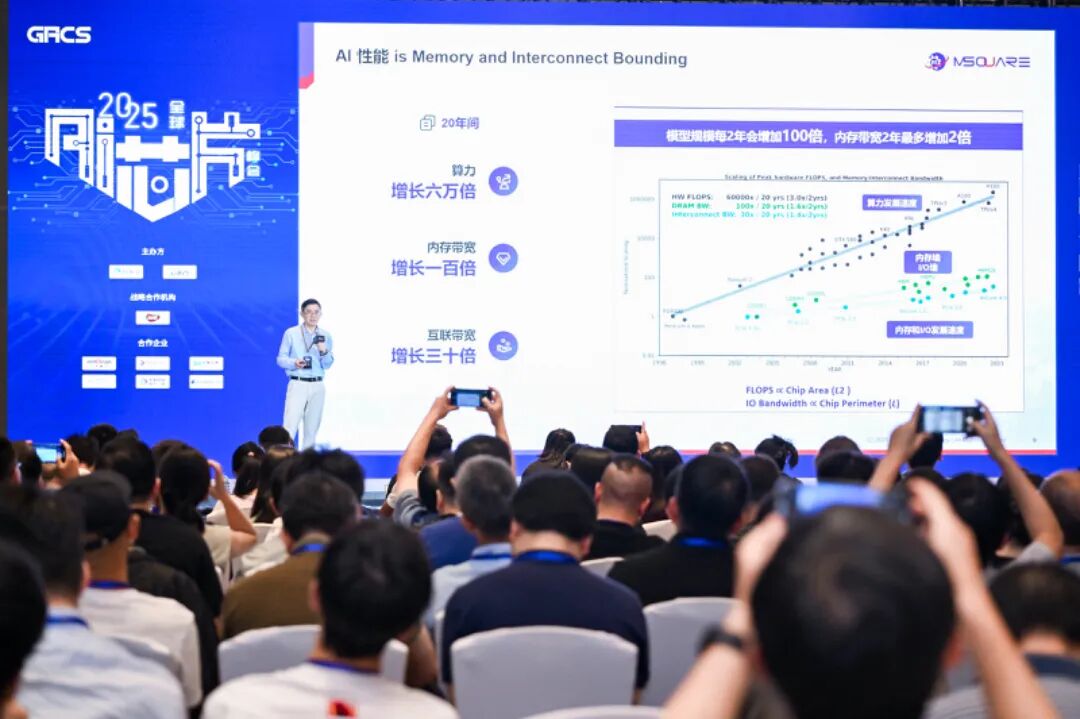

在主论坛的重量级演讲环节中,奎芯科技联合创始人兼副总裁唐睿博士带来主题演讲《Chiplet,AI算力的基石》。他指出,随着GPT-5、Gemini、Kimi等大模型进入万亿参数时代,传统SoC架构在工艺、良率、带宽和功耗上的瓶颈日益凸显。Chiplet作为新一代架构范式,正在通过模块化与异构集成重塑算力平台,而决定其成败的关键在于芯粒间的高效互联。唐睿强调,开放的UCIe标准正在成为产业共识,它将推动AI算力平台由封闭走向协同,让不同厂商和生态能够在统一接口下快速实现芯片集成。

会上,奎芯科技正式介绍了其32Gbps标准封装UCIe IP解决方案。该方案已成功完成硅验证,在25mm的基板互连距离上实现了稳定传输,并集成完整的控制器与物理层IP组合,能够为AI SoC客户提供高带宽、低延迟且可靠的Die-to-Die互联能力。与会专家指出,这一方案不仅突破了互连瓶颈,还因其兼容标准基板封装,大幅降低了系统复杂度与制造成本,具备广泛的量产导入价值。

除了接口IP,奎芯科技还在现场展示了ML100 IO Die。该产品通过UCIe接口实现HBM3与SoC的解耦,单模块带宽高达819.2GB/s,在显著提升系统灵活性的同时,有效降低了2.5D封装成本,并支持基于国产供应链的高度定制化,受到与会嘉宾的高度关注。这标志着奎芯科技已在Chiplet商业应用上实现了从接口IP到系统级产品的完整布局。

唐睿在演讲中进一步强调,过去十年行业关注的焦点在于算力本身,而未来十年,决定算力效率的关键将是“如何连接”。奎芯科技正以UCIe IP为核心起点,逐步构建全栈互连能力,覆盖接口IP、IO Die和相关互联产品方案,同时还在积极布局光电融合互联、3D存储base die等创新方向,推动AI硬件基础设施向更高能效与更强灵活性演进。

作为峰会的重要亮点,主办方智东西与芯东西多年来持续深耕半导体与AI产业报道,凭借独立视角与行业影响力,为产学研搭建了深度交流的平台。通过智猩猩等子品牌的运营,主办方不仅推动了国内AI芯片生态的传播与认知,也在全球范围内树立了中国AI产业的专业窗口。

凭借在高速接口IP与Chiplet互联上的持续突破,奎芯科技正在成长为AI算力基础设施的核心推动者。未来,公司将继续深化在UCIe、HBM、LPDDR等关键技术上的研发,携手产业链伙伴,共同构建开放、标准化、可扩展的Chiplet生态,助力中国乃至全球AI芯片产业在大模型时代实现加速突破。